01D’abord le concept

I2C est connu sous le nom d’inter – Integrated Circuit, littéralement entre circuits intégrés, ou I2C bus.Il s’agit d’un bus de communication série utilisant une architecture maître – esclave multiple, développée dans les années 80 par Philips Corporation (société mère de NXP NXP) pour les cartes mères, les systèmes embarqués pour connecter les périphériques à basse vitesse.

I2C se compose de deux lignes de fuite ouvertes bidirectionnelles, ce qui est un grand avantage et le câblage est simple.Les deux lignes tirent le potentiel vers le haut en utilisant la résistance de pull – up.Les potentiels typiques sont + 3,3 V ou + 5 v.Le taux de transfert standard est de 100kb / s et le mode basse vitesse est de 10kb / S.

02Couche physique

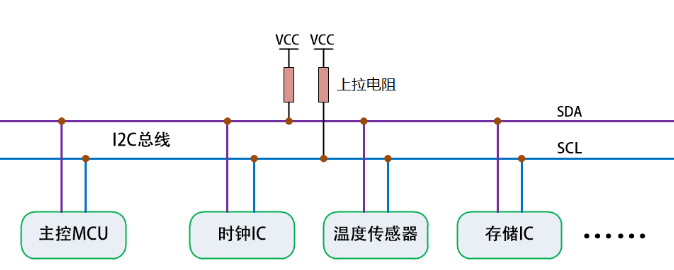

L’image ci – dessous est une topologie physique du bus I2C, vous pouvez voir qu’il n’y a que deux bus, une ligne de données SDA (Serial Data) pour transporter les données et une ligne d’horloge SCL (Serial Clock line) pour contrôler l’ordre d’émission et de réception des données.Tous les périphériques I2C ont reçu le SDA sur le bus et SCL sur le SCL du bus.Chaque appareil a sa propre adresse unique pour garantir l’exactitude de l’accès entre les appareils.

La connexion I2C à la couche physique est sans doute très simple, ce qui est également son plus grand avantage, le principe étant de produire les signaux nécessaires au Protocole de bus I2C pour la transmission de données en contrôlant la synchronisation des niveaux bas et bas des lignes SDA et SCL.SCL et SDA sont tirés vers le haut par la résistance de pull – up pendant que le bus est au repos, restant à un niveau haut.

Il est important de noter que I2C communique en semi – duplex, car il n’y a qu’une seule ligne de données et qu’à un moment donné, il n’est possible de communiquer qu’à sens unique.Cela montre également que I2C n’est pas adapté aux applications de transmission de gros volumes de données.

La distinction entre hôte, esclave est simple, c’est l’hôte qui émet la commande principale, c’est l’esclave qui reçoit la commande, le même bus I2C permet la présence de plusieurs hôtes.

03Couche de protocole

Comme base, nous commençons par comprendre quelques petits concepts importants.

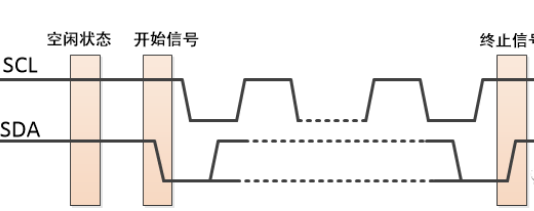

1,État initial(c’est – à – dire l’état inactif): le niveau haut résultant de la résistance de traction montante SDA et SCL est l’état initial;

2,Signal de début: le SDA est tiré vers le bas lorsque SCL est au niveau haut, ce qui est un signal de début indiquant le début de la communication.

3,Signal de terminaison: lorsque SCL est au niveau haut, le SDA est relevé, ce qui est un signal de terminaison indiquant la fin de cette communication.

Est – ce que tout le monde a trouvé quelque chose ici?Lorsque SCL est au niveau haut, le niveau SDA est un signal dès qu’il change, soit pour commencer, soit pour se terminer.Donc dansPendant le transfert de données,SCL est au niveau haut, SDA doit rester stable et ne peut changer que si SCL est au niveau bas SDA.

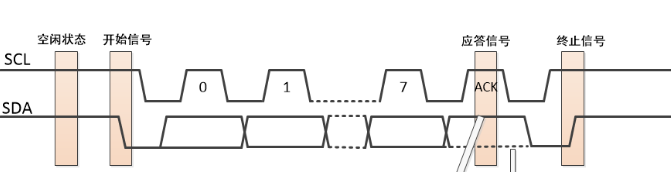

4,Signal de réponse: lorsque l’émetteur a fini d’envoyer un octet / 8 bits de données au récepteur, au cours du 9ème cycle d’horloge, le récepteur doit donner un signal de réponse à l’émetteur pour que les données soient considérées comme une transmission réussie.Le compteur de haut niveau ne répond pas, le compteur de bas niveau répond.

Une fois que nous avons compris ces quelques états de signal, regardez étape par étape comment les données sont transmises.

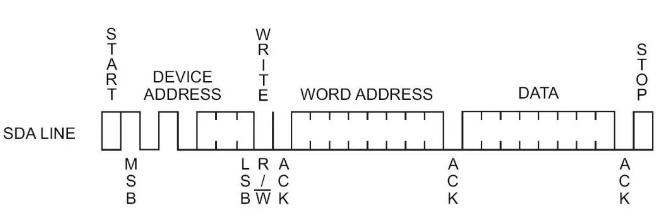

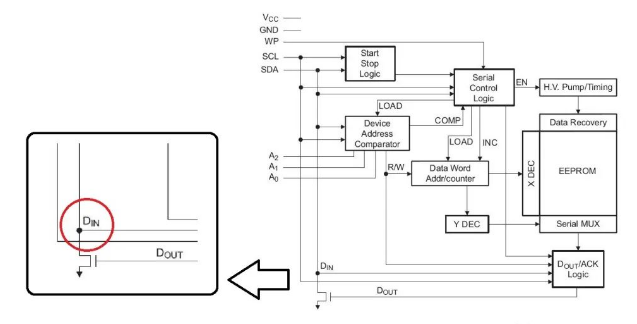

Écrire un octet de données dans un certain registre du dispositif esclave: signal de début + adresse du dispositif (7 bits) + lecture / écriture (1 bit) + attente de la réponse esclave + adresse du registre (8 bits) + attente de la réponse esclave + données à écrire (8 bits) + attente de la Réponse esclave + signal de fin.La figure suivante est un chronogramme des données d’écriture de la mémoire EEPROM 24c02.

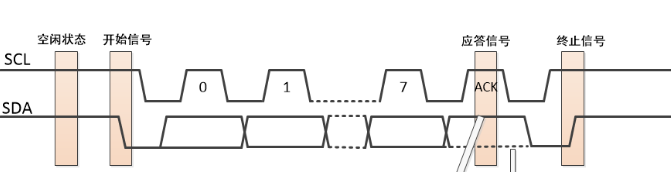

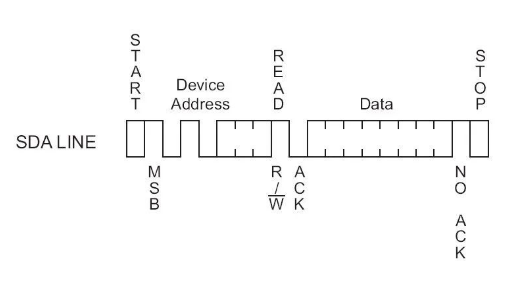

2, écrivez que nous avons vu, alors lisez un essai: l’image ci – dessous est un chronogramme de lecture d’un octet de données pour l’adresse actuelle 24c02, n’est – ce pas en un coup d’œil.Il est à noter que le BIT d’état de lecture et d’écriture après l’adresse 7 bits lors de la lecture est 1.Voici pourquoi enfin no ACK, dans l’Opération « read », l’hôte est le récepteur et le No ACK de l’hôte signifie qu’il cesse de recevoir les données de 24c02, sinon 24c02 continuera à émettre.

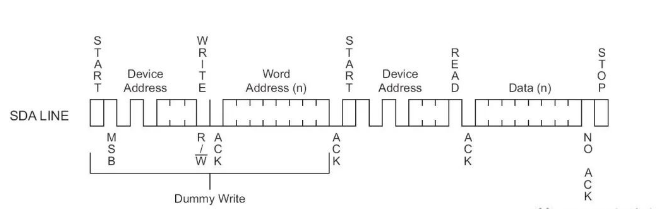

3, nous lisons un peu plus long: l’image ci – dessous est un chronogramme pour la lecture d’un octet de données à n’importe quelle adresse 24c02.Signal de départ + adresse du périphérique (7 bits) + écriture (1 bit) + attente d’une réponse esclave + adresse de données (8 bits) + attente d’une réponse esclave.Cette étape précédente est une fausse écriture, le but étant de dire à 24c02 quelles données d’adresse lire.Continuer, signal de début + adresse du périphérique (7 bits) + lecture (1 bit) + attente de la réponse de l’esclave + données lues (8 bits) + attente de la réponse de l’hôte (récepteur) + signal de fin.

04Réapprovisionnement de marchandises sèches

1,Adresse de l’appareilL’adresse du périphérique I2C est de 8 bits, mais le dernier BIT n’appartient pas à l’adresse lors de l’opération de synchronisation, mais à un bit d’état de lecture ou d’écriture.C’est pourquoi l’adresse de l’opération Curry sh1106 d’arduino n’est pas 0x7 – mais 0x3 -, car les 7 premiers bits sont utiles et l’adresse est traitée avec un décalage d’un bit vers la droite.Encore une fois, les quatre premiers bits de l’adresse du périphérique sont fixes et morts, et sont utilisés par les fabricants pour indiquer le type de périphérique, tels que l’interface I2C pour les quatre premiers bits de l’adresse du périphérique de type capteur de température généralement 1001 à savoir 9x, les quatre premiers bits de l’adresse de la mémoire EEPROM généralement 1010 à savoir ax, les quatre premiers bits de l’adresse de l’écran OLED généralement 0111 à savoir 7x, etc.

2,L’inconvénient mortel de l’interface I2C est la vitesse de transmission lente près de la distance simultanée– Oui.Tout le monde lors de l’utilisation de l’interface de bus I2C, rappelez – vous de ne pas transmettre de longues lignes, essayez de ne transférer que dans la carte PCB, sinon perdre des données occasionnelles ou même ne pas lire les données fera planter les gens, ne me demandez pas comment je sais, demandez seulement des larmes.

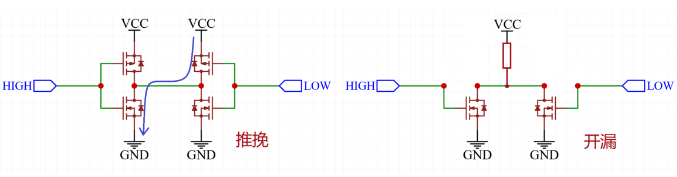

3,À propos pourquoi deux lignes sont conçues pour ouvrir les fuitesJe me souviens d’avoir déjà enterré un stylo voltigeur lors de l’écriture de 8 modes de fonctionnement pour les E / S stm32.Une raison précise aujourd’hui.Il y a principalement deux points ① pour éviter les courts – Circuits: pensez que si vous n’êtes pas configuré pour ouvrir des fuites, mais pour pousser et pull, plusieurs périphériques sont connectés au même bus, c’est – à – dire qu’un certain io d’un périphérique produit un niveau haut et un autre io produit un niveau bas, vous trouverez que les VCC et GNd de ces deux io sont court – circuités;Mais les fuites ouvertes n’auront pas ce problème, comme illustré ci – dessous:

La deuxième raison est « line and », nous pensons à un scénario: si un périphérique a sur le bus tire le SDA haut, alors qu’un autre périphérique B sur le bus a tiré le SDA bas, alors parce que 1 & 0 = 0, le périphérique a vérifie le SDA et trouve que ce n’est pas Le niveau haut mais le niveau bas, ce qui indique qu’il y a déjà d’autres périphériques sur le bus qui occupent le bus,A doit abandonner, si la détection est de niveau élevé, il peut être utilisé.L’image ci – dessous est un schéma interne de la puce 24c02, vous pouvez voir le pied de détection d’état.

05Résumé

Le bus I2C, en tant que Protocole de bus commun, vaut la peine d’être soigneusement étudié, ce qui nous permettra d’utiliser n’importe quel périphérique d’interface I2C plus tard.J’ai toujours eu l’impression que dans le processus d’apprentissage, « utiliser» n’est pas nécessairement la fin de notre quête, et que le fait d’utiliser quelque chose de plus profond et de le comprendre en même temps procure une joie inattendue.